Verilog code for an 8-bit shift-left register with a positive-edge clock, serial in and serial out.

Verilog code for an 8-bit shift-left register with a negative-edge clock, a clock enable, a serial in and a serial out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, asynchronous clear, serial in and serial out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, a synchronous set, a serial in and a serial out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, a serial in and a parallel out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, an asynchronous parallel load, a serial in and a serial out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, a synchronous parallel load, a serial in and a serial out.

Verilog code for an 8-bit shift-left/shift-right register with a positive-edge clock, a serial in and a serial out.

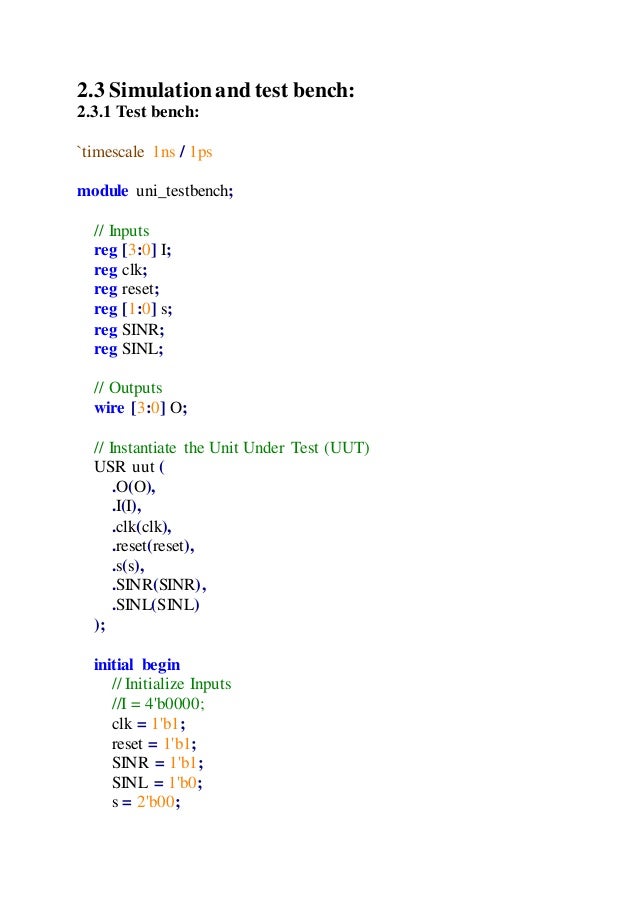

Universal Shift Register Verilog Code

I am learning and practicing Verilog HDL. I wanted to design a 16 bit parallel in series out shift register. Module verilogshiftregistertestPISO( din, clk, load, dout ); output reg dout; i. IC 74498 8-bit bidirectional shift register with parallel inputs and three-state outputs. IC 74671 4-bit bidirectional shift register. IC 74673 16-bit serial-in serial-out shift register with output storage registers. IC 74674 16-bit parallel-in serial-out shift register with three-state outputs. In these ICs, mostly used are. From Wikibooks, open books for an open world. new data to shift in Output: out stdlogicvector (3 downto 0); Input:. Title: Verilog Code For 8 Bit Parallel In Serial Out Shift Register.JK Shift Register S/R 6-Bit Shift Register 4-Bit Parallel Access Shift Register 4-Bit. 4bit parallel access shift register at. Parallel or serial.

Shift In Verilog

Shift Register In Verilog

- Verilog code Saturday, 4 July 2015. Output dout; input din. // File: Serial IN Parallel OUT Shift Register using Behavior Modeling Style.v.

- PAROUT should be a registered output and therefore should never be assigned in a combinational block (ie always @(.)). What you need to do is move all the PAROUT code up to the always @(posedge) block into the appropriate place. Also, don't assign to a bit, but instead shift the serial value in (ie.